失くしちゃいけないメモ書き(原著者Petteri Aimonenさん了解で日本語ページ作成しました) |

||

| ”DSO

Quad"メニューへ

|

USBのプロトコルアナライザ

|

|

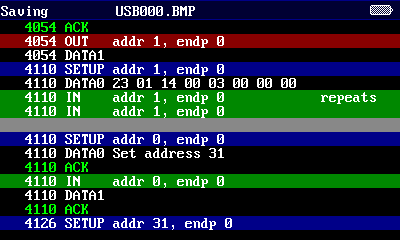

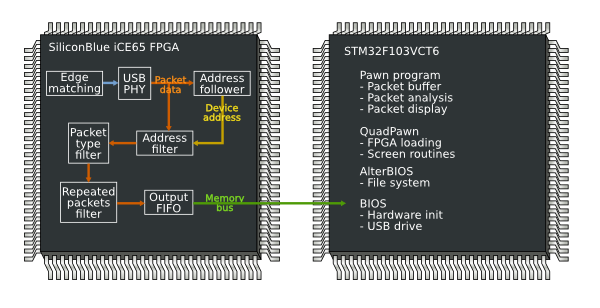

FPGA論理USBプロアナの処理の多くはFPGAで動きます。FPGAが受信してUSBのプロトコルをデコードし、限られたRAMメモリーを使いこなすため、パケットをフィルターします。こんだけのことをFPGAの上でやっても4000素子中の1300しか使いませんでした。 FPGAコードの中で最も面白いのはおそらく繰り返しフィルタです。これはパケットの繰り返しシーケンスを節約するためで、例えば「IN,NAK]などはホストがデータをポーリングするときに発生します。FPGA上で可変長パケットを処理するのはそんなに簡単なものではありません。しかし2レベルの設計法でこの問題を何とか解決しました。 |

||

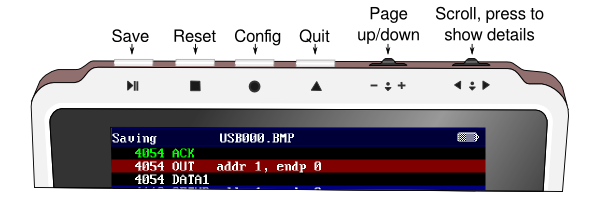

使い方ここからプログラムをダウンロードしてください。ソースコードはこっちです。このプログラムを走らせるためにはQuadPawnの0.06より新しいコードが必要です。それは同じページからダウンロードできます。インストールするためにはusb.amxとusb.fpgをUSBのメモリーにQuadPawnが走っているときにコピーしてください。そして再投入するとメニューが現れます。

このプログラムを使うために何とかしてUSB信号線にプローブをつなぎます。簡単な方法としてはUSB延長ケーブルから何らかの方法で取り出します。CH-AをD-につなぎ、CH-BにはD+を繋がないといけません。繋いで見ると画面に何かパケットが現れるはずです。 |

||

制限

|

||